Intel C220 Chipsets

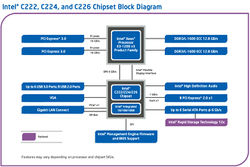

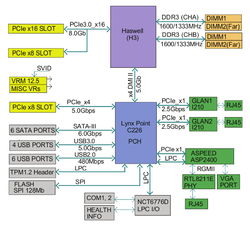

Intel C220 Chipsets (Codename Lynx Point) are used in Single-CPU Servers and Workstation Motherboards for Intel Xeon E3-1200 v3 CPUs (Haswell Micro-architecture). They are the successors of the C200 Chipsets that are used for Sandy Bridge and Ivy Bridge Intel Microarchitectures CPUs.

An Overview of the C220 Chipset

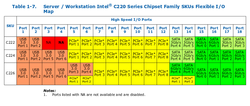

The C220 series consists of three chipsets:

| C222 | C224 | C226 | |

|---|---|---|---|

| Flexible I/O | - | - | ✔ |

| PCI Express 2.0 Ports | 8 | 8 | 8 |

Total number of USB Ports

|

10 2 8 |

12 4 8 |

14 4-6(*) 10-8(*) |

Total number of SATA Ports

|

6 2 4 |

6 4 2 |

4-6(*) 4-6(*) 0 |

| VGA | - | - | ✔ |

| Intel Wireless Display | - | - | ✔ |

| Intel Rapid Storage Technology - AHCI | ✔ | ✔ | ✔ |

| Intel Rapid Storage Technology - RAID 0/1/5/10 Unterstützung | ✔ | ✔ | ✔ |

| Intel Rapid Storage Technology - Intel Smart Response Technology | - | - | ✔ |

| Intel Active Management Technology 9.0 | - | - | ✔ |

| Intel Identity Protection Technology (Intel IPT) | - | - | ✔ |

(*) depending on Flexible I/O configuration of the motherboard designer

New Features compared to the C200

The Intel C220 chipset generation offers the following new features:[1]

- USB 3.0

- Intel Flexible I/O

- Intel Rapid Storage Technology 2.0

- Up to 6x 6Gb/s SATA Ports

- PCI Express Latency Tolerance Reporting (LTR)

- The PCI Express Root Port supports LTR.

- The end device reports dynamically to the Root Port about their service latency requirements for memory access.

- Whenever the latency tolerance or the boot process is changed, the end device should transmit a new LTR message to the Root Port.

- The PCH uses this information to make better power management decisions.

- The processor selects the worst-case value from the tolerance values to optimize the transition between the energy states (C-states).

- This results in an improved power management without influencing the end device function.

- End devices that support LTR must implement the "reporting and enable mechanism" according to the PCIe Latency Tolerance Reporting Engineering Change Notice.

- New features of the Serial Peripheral Interface (SPI)

- Supports Quad IO Fast Read, Quad Output Fast Read, Dual IO Fast Read

- Support for TPM over SPI

- Supports Serial Flash Discoverable Parameter (SFDP)

References

- ↑ Intel® 8/C220 Series Chipset Platform Controller Hub: Datasheet (www.intel.com)

Additional Information

- Wandelbare Verwaltungsmaschine Das leistet die „Management Engine“ in Intel-Chipsätzen (c't 13/2014, Seite 138)

- Intel® Xeon® Processor E3-1200 v3 Product Family with Intel® HD Graphics P4600 and Intel® C226 Chipset (www.intel.com)

- Intel Xeon Processor E3-1200 v3 Product Family-based Platforms for Intelligent Systems (www.intel.com)

- 4th Generation Intel® Core™ Processor-Based Platforms for Intelligent Systems (www.intel.com)

- Haswell-based Xeon chipsets (en.wikipedia.org)

|

Author: Thomas Niedermeier Thomas Niedermeier working in the product management team at Thomas-Krenn, completed his bachelor's degree in business informatics at the Deggendorf University of Applied Sciences. Since 2013 Thomas is employed at Thomas-Krenn and takes care of OPNsense firewalls, the Thomas-Krenn-Wiki and firmware security updates.

|